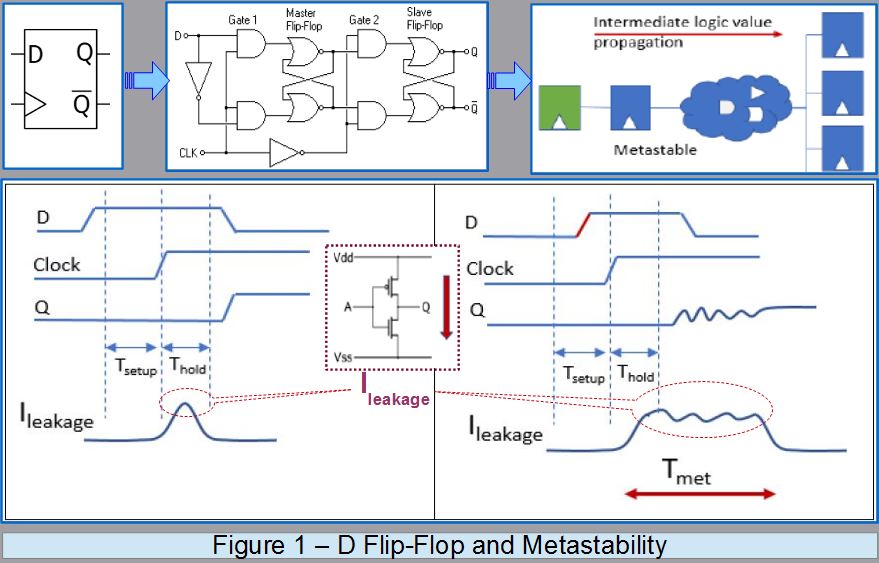

Synchronizers for Asynchronous Signals | David Fong's ASIC Architecture, Design, Verification and DFT Blog

Optical chaotic flip-flop operations with multiple triggering under clock synchronization in the VCSEL with polarization-preserved optical injection